# Barramentos ISA, EISA, VLB, PCI e AGP

Copyright © 2001 Walter Fetter Lages

1

## XT-bus

- 8 bits de dados

- 16 bits de endereços

- Clock 4.77MHz

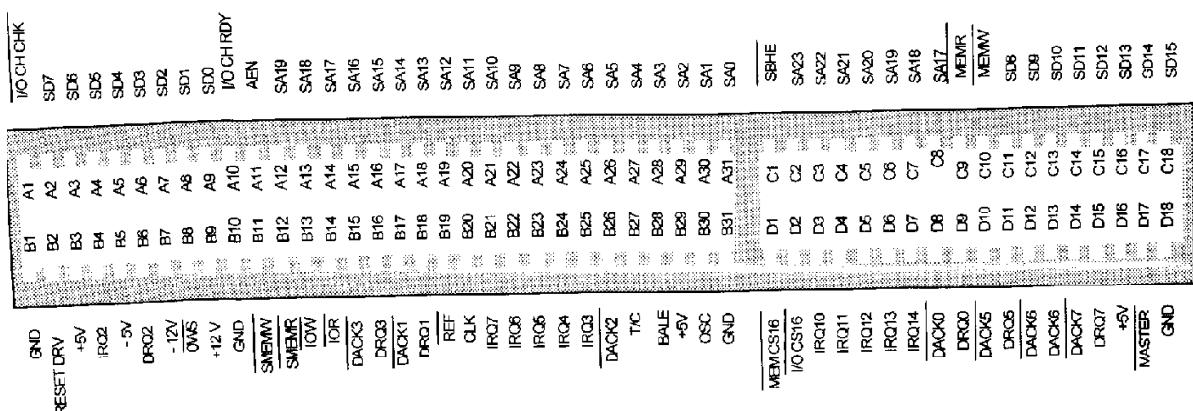

|           |     | I/O CH CHK |

|-----------|-----|------------|

| GND       | A1  | SD7        |

| RESET DRV | A2  | SD6        |

| +5V       | A3  | SD5        |

| IRQ2      | A4  | SD4        |

| -5V       | A5  | SD3        |

| DRQ2      | A6  | SD2        |

| -12V      | A7  | SD1        |

| 0WS       | A8  | SD0        |

| +12 V     | A9  | I/O CH RDY |

| GND       | A10 | AEN        |

| SMEMW     | A11 | SA19       |

| SMEMR     | A12 | SA18       |

| IOW       | A13 | SA17       |

| IOR       | A14 | SA16       |

| DACK3     | A15 | SA15       |

| DRQ3      | A16 | SA14       |

| DACK1     | A17 | SA13       |

| DRQ1      | A18 | SA12       |

| REF       | A19 | SA11       |

| CLK       | A20 | SA10       |

| IRQ7      | A21 | SA9        |

| IRQ6      | A22 | SA8        |

| IRQ5      | A23 | SA7        |

| IRQ4      | A24 | SA6        |

| IRQ3      | A25 | SA5        |

| DACK2     | A26 | SA4        |

| T/C       | A27 | SA3        |

| ALE       | A28 | SA2        |

| +5V       | A29 | SA1        |

| OSC       | A30 |            |

| GND       | A31 |            |

Copyright © 2001 Walter Fetter Lages

2

# XT-bus

- +5V, -5V, +12V, -12V

- 6 níveis de interrupção

- 3 canais de DMA

- Oscilador de 14.31818 MHz (clock x 3)

- Driver de reset

- Sinal 0 Wait-states

Copyright © 2001 Walter Fetter Lages

3

## Industry Standard Architecture

- 8/16 bits de dados

- 24 bits de endereços

- Clock de 8MHz

- Suporte a bus-master

- 7 canais de DMA

- 10 níveis de interrupção

Copyright © 2001 Walter Fetter Lages

4

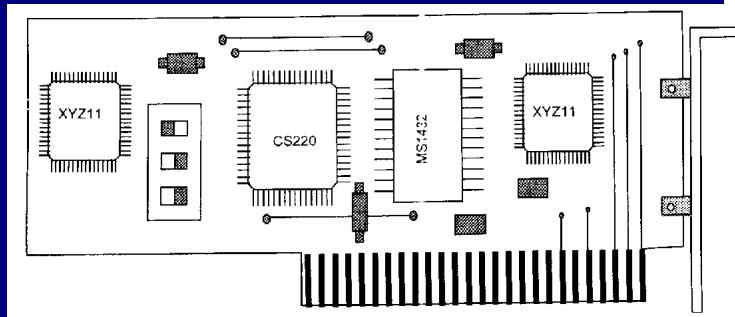

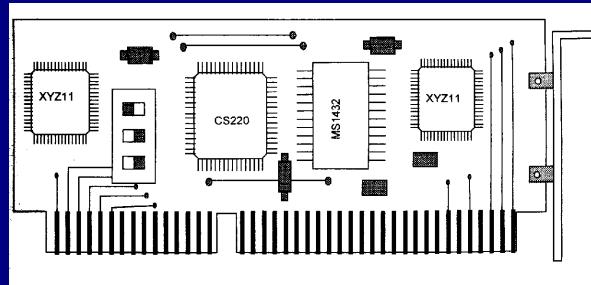

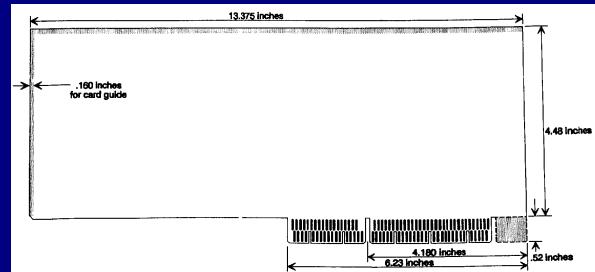

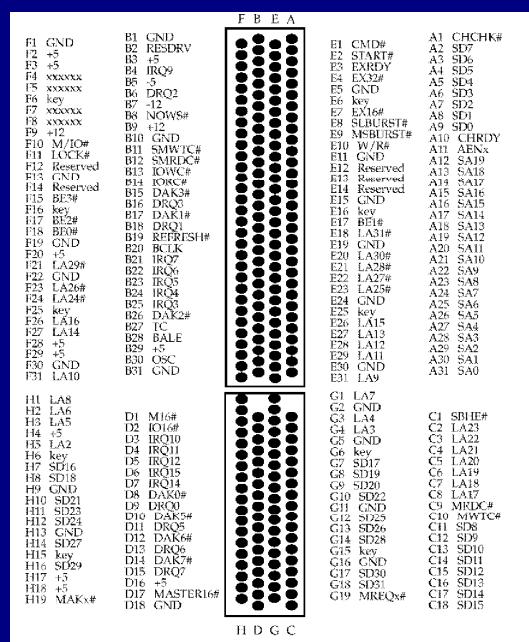

# Slot ISA

Copyright © 2001 Walter Fetter Lages

5

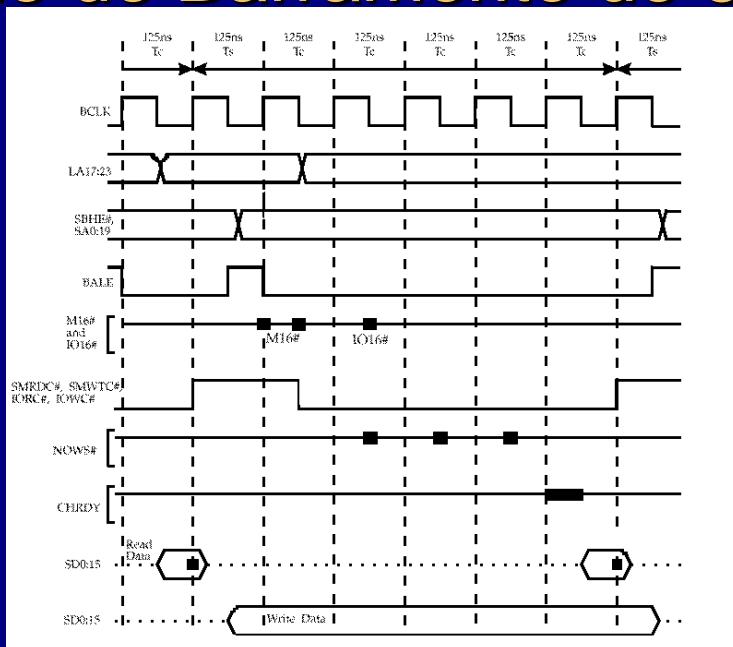

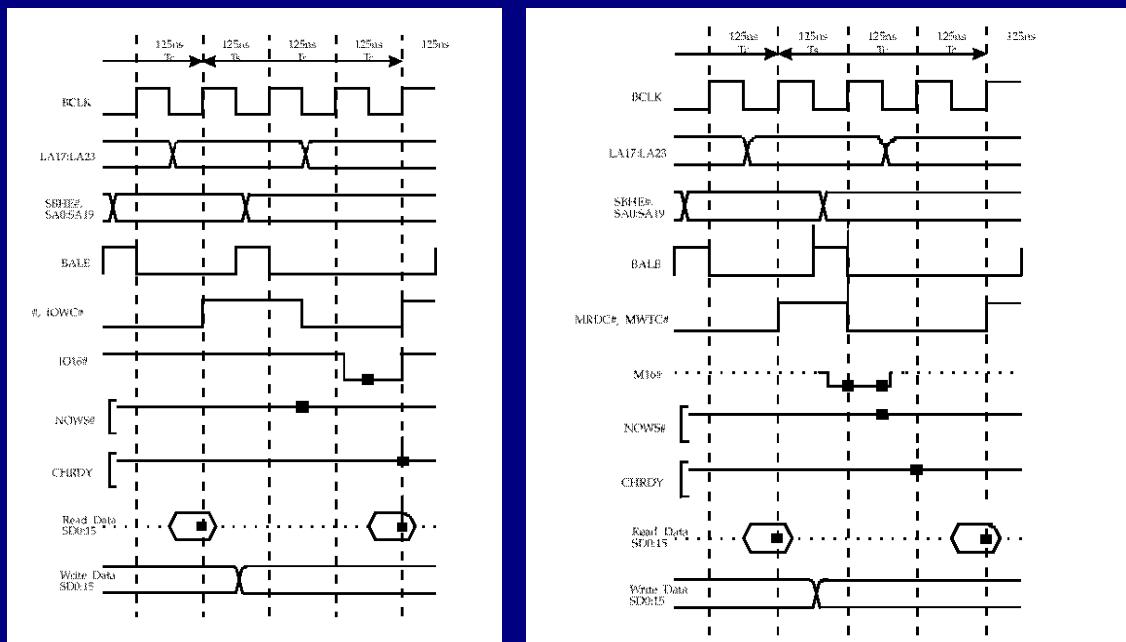

## Ciclo de Barramento de 8 bits

Copyright © 2001 Walter Fetter Lages

6

# Ciclo de Barramento de 16 bits

Copyright © 2001 Walter Fetter Lages

7

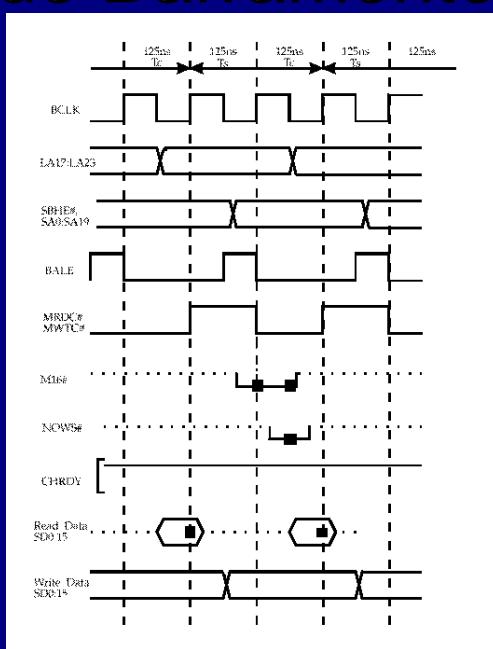

# Ciclo de Barramento 0 WS

Copyright © 2001 Walter Fetter Lages

8

# Enhanced ISA (EISA)

- 32 bits de dados

- 32 bits de endereços

- Clock de 8.33MHz

- Bus-master

- Arbitragem

- Configuração automática

- Interrupções nível ou borda compartilháveis

- DMA compartilhável

Copyright © 2001 Walter Fetter Lages

9

## EISA

- Lock do barramento

- Espaço de I/O específico para cada slot

Copyright © 2001 Walter Fetter Lages

10

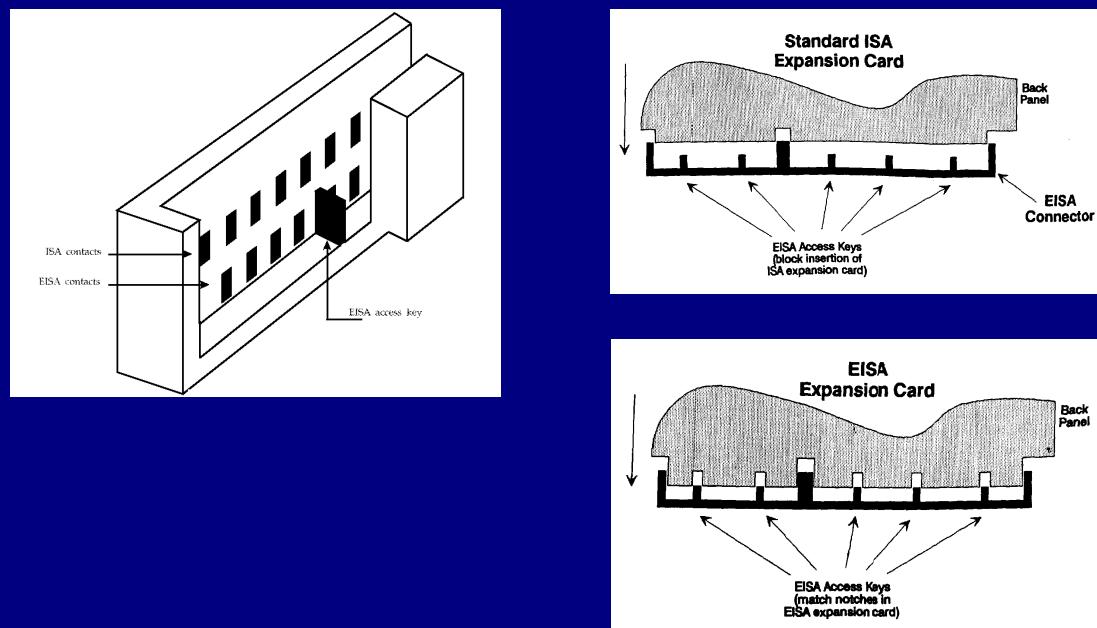

# Slot EISA

Copyright © 2001 Walter Fetter Lages

11

## Pinagem EISA

Copyright © 2001 Walter Fetter Lages

12

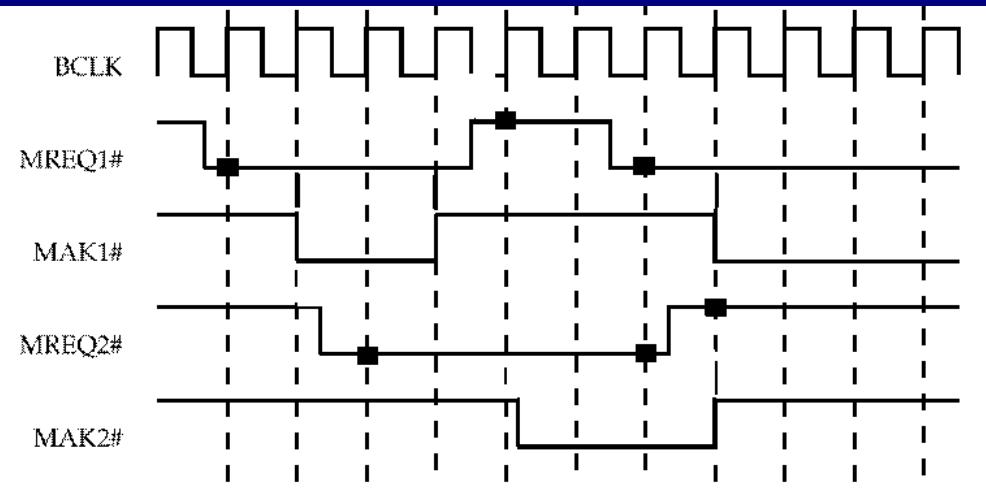

# Arbitragem

Copyright © 2001 Walter Fetter Lages

13

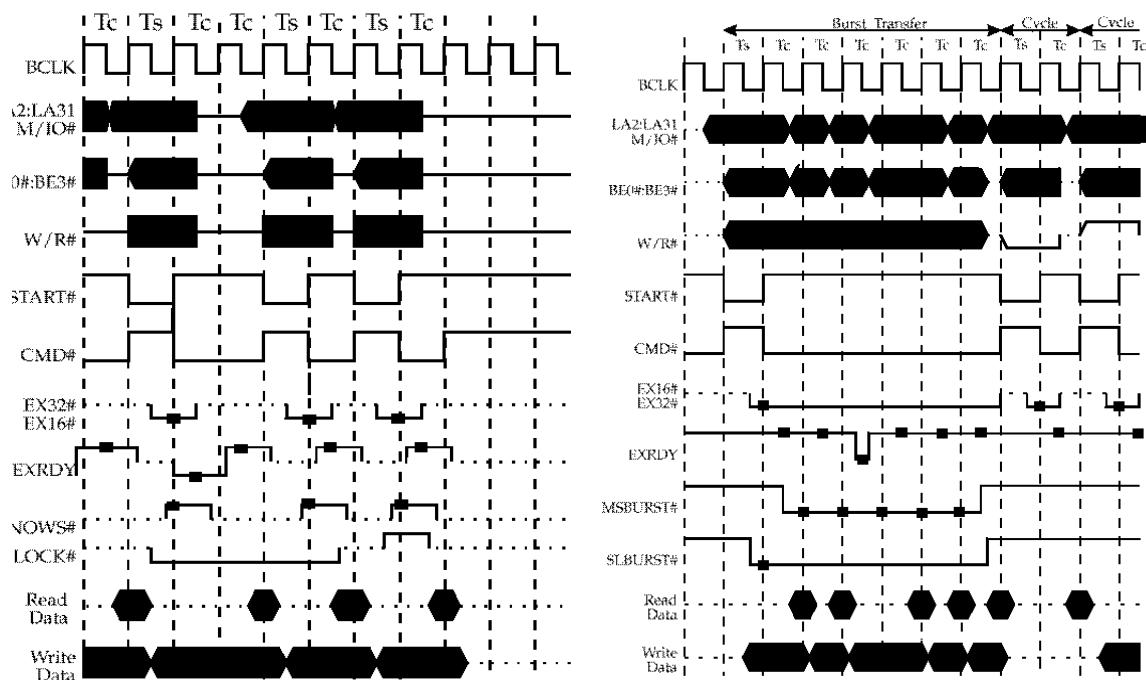

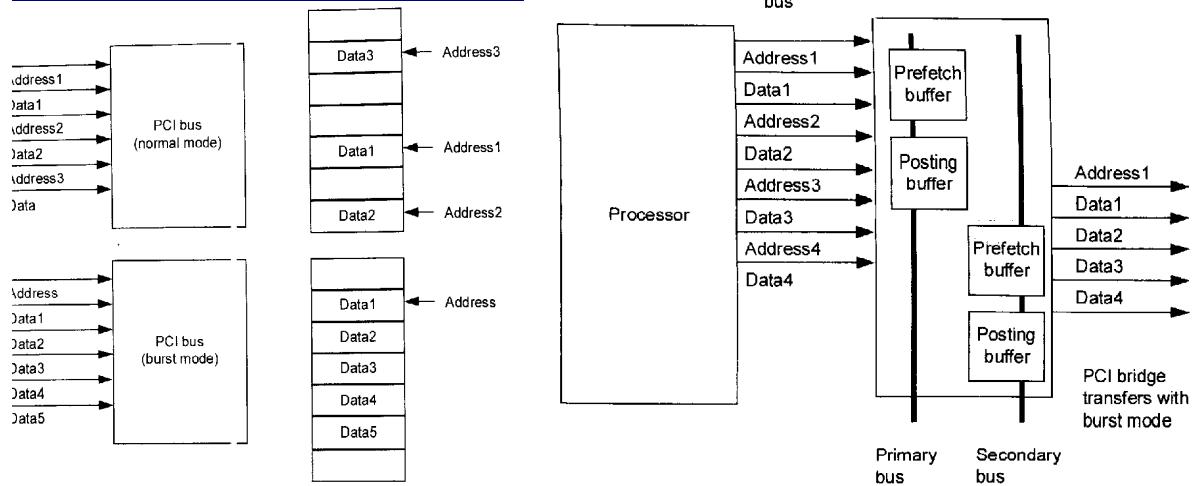

## Ciclo Padrão/Burst

Copyright © 2001 Walter Fetter Lages

14

# Mapeamento de I/O

| Range (hex)              | Reserved For                       | Range Reserved For |

|--------------------------|------------------------------------|--------------------|

| 0000 – 00FF              | EISA /ISA system board I/O devices | System Board       |

| 0100 – 03FF              | ISA expansion cards                | ISA cards          |

| 0400 – 04FF              | EISA system board I/O              | System Board       |

| 0500 – 07FF              | alias of ISA range; do not use     |                    |

| 0800 – 08FF              | EISA system board I/O              | System Board       |

| 0900 – 0BFF              | alias of ISA range; do not use     |                    |

| 0C00 – 0CFF              | EISA system board I/O              | System Board       |

| 0D00 – 0FFF              | alias of ISA range; do not use     |                    |

| 1000 – 10FF              | Slot 1 I/O                         | EISA slot one      |

| 1100 – 13FF              | alias of ISA range; do not use     |                    |

| 1400 – 14FF              | Slot 1 I/O                         | EISA slot one      |

| 1500 – 17FF              | alias of ISA range; do not use     |                    |

| 1800 – 18FF              | Slot 1 I/O                         | EISA slot one      |

| 1900 – 1BFF              | alias of ISA range; do not use     |                    |

| 1C00 – 1CFF              | Slot 1 I/O                         | EISA slot one      |

| 1D00 – 1FFF              | alias of ISA range; do not use     |                    |

| 2000 – 20FF              | Slot 2 I/O                         | EISA slot two      |

| 2100 – 23FF              | alias of ISA range; do not use     |                    |

| 2400 – 24FF              | Slot 2 I/O                         | EISA slot two      |

| 2500 – 27FF              | alias of ISA range; do not use     |                    |

| 2800 – 28FF              | Slot 2 I/O                         | EISA slot two      |

| 2900 – 2BFF              | alias of ISA range; do not use     |                    |

| 2C00 – 2CFF              | Slot 2 I/O                         | EISA slot two      |

| 2D00 – 2FFF              | alias of ISA range; do not use     |                    |

| repeated for every X000– |                                    |                    |

Copyright © 2001 Walter Fetter Lages

15

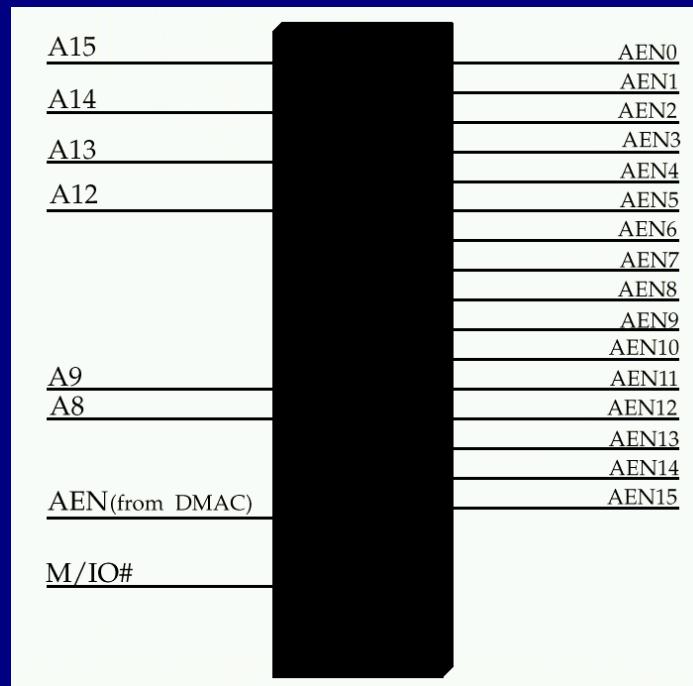

# Decodificador de AEN

Copyright © 2001 Walter Fetter Lages

16

# Configuração

- Identificador de produto

- Código ASCII

- obtido nos endereços xC80h–xC83h

- 3 caracteres alfabéticos especificam o fabricante

- 4 caracteres numéricos especificam o produto

- Pseudo switches

- Localizados no espaço de endereço específico

- Utilizados para configuração automática

- Arquivos de configuração

- !del1234.cfg

- !cpq0010.cfg

- !ibm4567.cfg

Copyright © 2001 Walter Fetter Lages

17

## VESA Local Bus

- 32 bits de dados

- 32 bits de endereços

- 25–40MHz

- Bus-master

- Limitado a 2 ou 3 slots

- Extensão dos sinais do 80386 para um slot

Copyright © 2001 Walter Fetter Lages

18

# Pinagem VLB

| Back Side | Component Side | Back Side   | Component Side |

|-----------|----------------|-------------|----------------|

| B1 Dat00  | A1 Dat01       | B30 Adr17   | A30 Adr16      |

| B2 Dat02  | A2 Dat03       | B31 Adr15   | A31 Adr14      |

| B3 Dat04  | A3 GND         | B32 Vcc     | A32 Adr12      |

| B4 Dat06  | A4 Dat05       | B33 Adr13   | A33 Adr10      |

| B5 Dat08  | A5 Dat07       | B34 Adr11   | A34 Adr08      |

| B6 GND    | A6 Dat09       | B35 Adr09   | A35 GND        |

| B7 Dat10  | A7 Dat11       | B36 Adr07   | A36 Adr06      |

| B8 Dat12  | A8 Dat13       | B37 Adr05   | A37 Adr04      |

| B9 Vcc    | A9 Dat15       | B38 GND     | A38 WBACK#     |

| B10 Dat14 | A10 GND        | B39 Adr03   | A39 BEO#       |

| B11 Dat16 | A11 Dat17      | B40 Adr02   | A40 Vcc        |

| B12 Dat18 | A12 Vcc        | B41 n/c     | A41 BE1#       |

| B13 Dat20 | A13 Dat19      | B42 RESET#  | A42 BE2#       |

| B14 GND   | A14 Dat21      | B43 DC#     | A43 GND        |

| B15 Dat22 | A15 Dat23      | B44 M/ID#   | A44 BE3#       |

| B16 Dat24 | A16 Dat25      | B45 W/R#    | A45 ADS#       |

| B17 Dat26 | A17 GND        |             |                |

| B18 Dat28 | A18 Dat27      |             |                |

| B19 Dat30 | A19 Dat29      | B48 RDYRTN# | A48 LRDY#      |

| B20 Vcc   | A20 Dat31      | B49 GND     | A49 LDEV<xx>   |

| B21 Adr31 | A21 Adr30      | B50 IRQ9    | A50 LREQ<xx>   |

| B22 GND   | A22 Adr28      | B51 BRDY#   | A51 GND        |

| B23 Adr29 | A23 Adr26      | B52 BLAST#  | A52 LGNT<xx>   |

| B24 Adr27 | A24 GND        | B53 ID0     | A53 Vcc        |

| B25 Adr25 | A25 Adr24      | B54 ID1     | A54 ID2        |

| B26 Adr23 | A26 Adr22      | B55 GND     | A55 ID3        |

| B27 Adr21 | A27 Vcc        | B56 LCLK    | A56 ID4        |

| B28 Adr19 | A28 Adr20      | B57 Vcc     | A57 LKEN#      |

| B29 GND   | A29 Adr18      | B58 LBS16#  | A58 LEAD5#     |

Copyright © 2001 Walter Fetter Lages

19

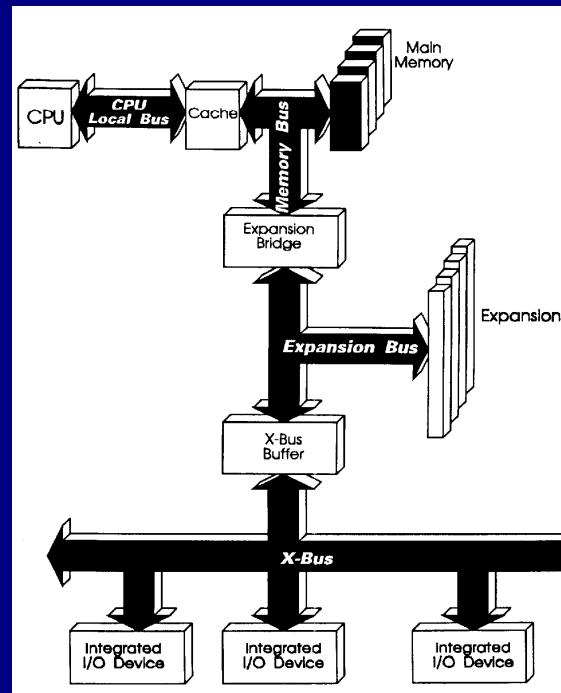

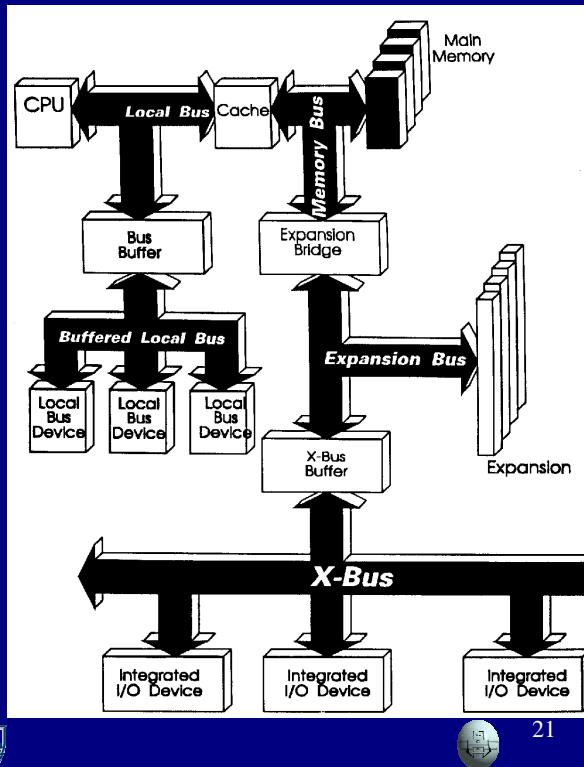

## X-bus

- Extensão bufferizada do barramento de expansão onde são conectados os dispositivos *on-board*

- Taxa de transferência limitada

Copyright © 2001 Walter Fetter Lages

20

# Barramento Local

- Interface dependente do processador utilizado.

- Não permite concorrência

Copyright © 2001 Walter Fetter Lages

21

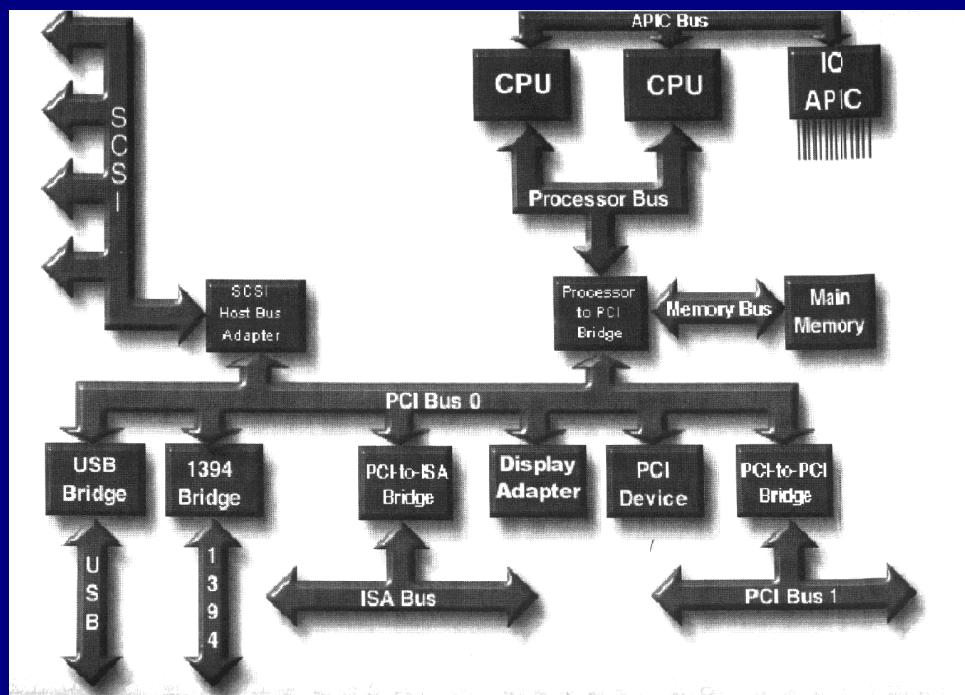

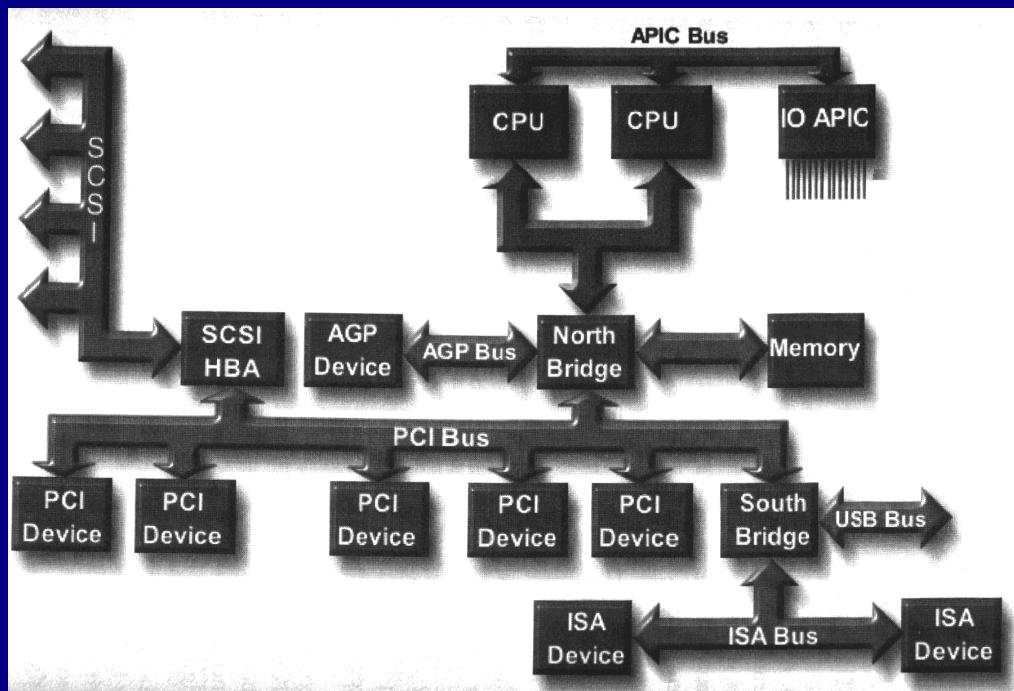

## Peripheral Component Interconnect (PCI)

- Operação independente do processador

- 32 bits de dados (extensão para 64 bits)

- 32 bits de endereços (extensão para 64 bits)

- Suporta bus-master

- Arbitragem oculta

- Paridade

- Três espaços de endereçamento

- Configuração automática

Copyright © 2001 Walter Fetter Lages

22

# PCI

- Clock de 33MHz (extensão para 66MHz)

- 4 níveis de interrupção

- Pode-se ter um sistema com vários barramentos PCI interconectados através de bridges PCI/PCI

- Todos os barramentos são tratados de forma uniforme pela configuração automática

Copyright © 2001 Walter Fetter Lages

23

## Arquitetura do Sistema PCI

Copyright © 2001 Walter Fetter Lages

24

# Slots PCI

Copyright © 2001 Walter Fetter Lages

25

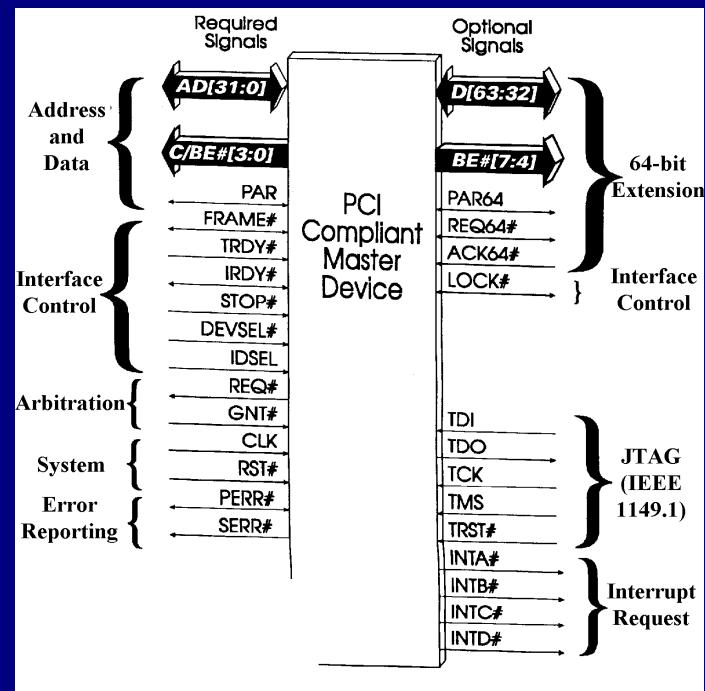

## Sinais PCI – Master

Copyright © 2001 Walter Fetter Lages

26

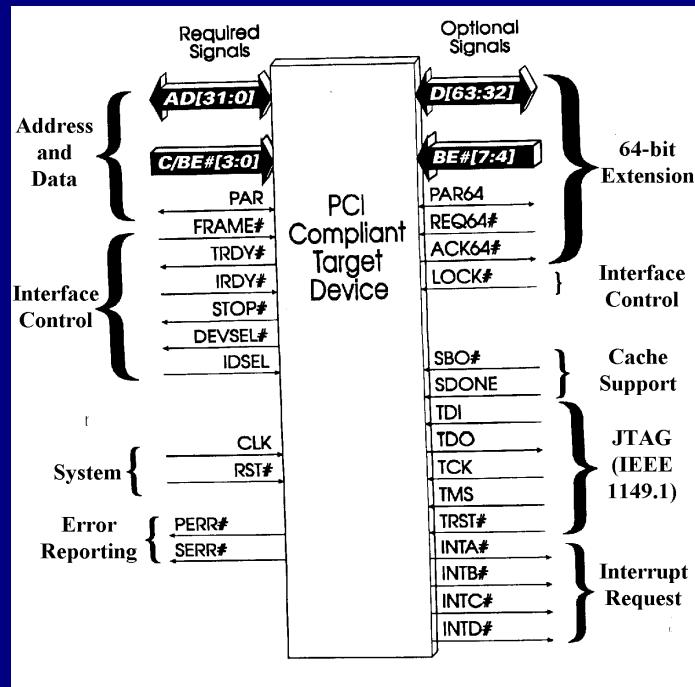

# Sinais PCI – Target

Copyright © 2001 Walter Fetter Lages

27

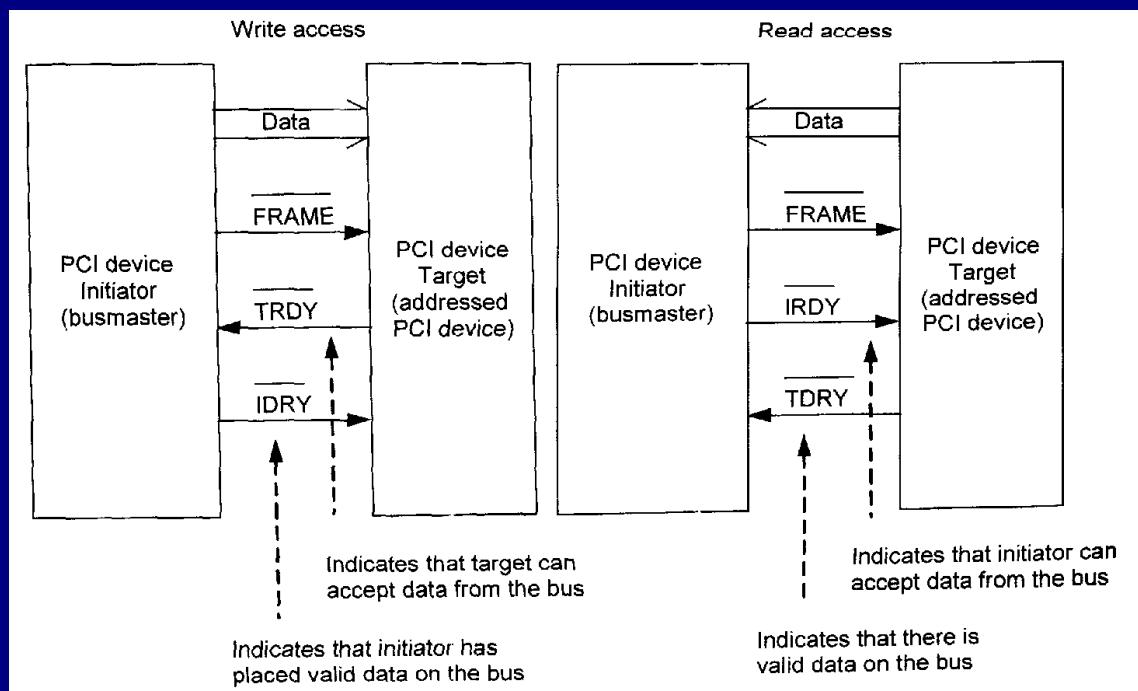

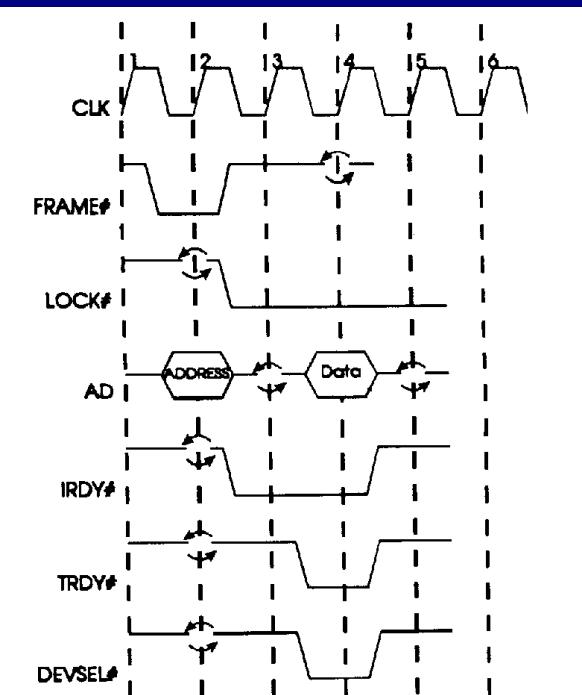

## Handshaking

Copyright © 2001 Walter Fetter Lages

28

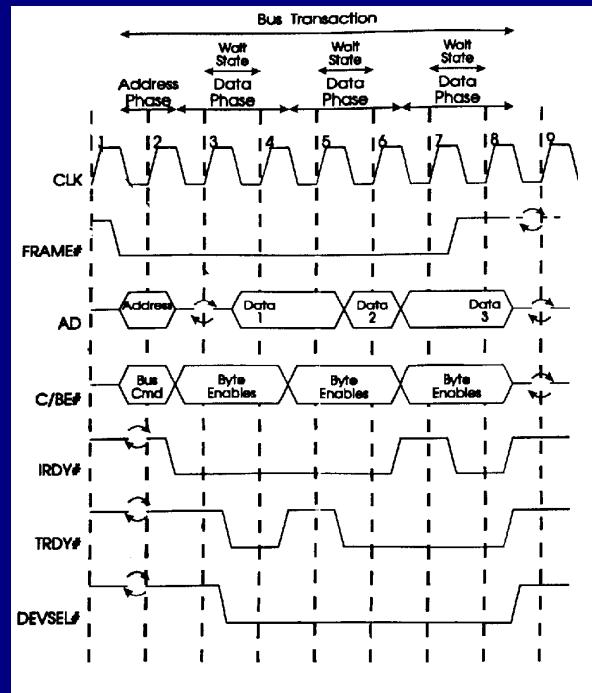

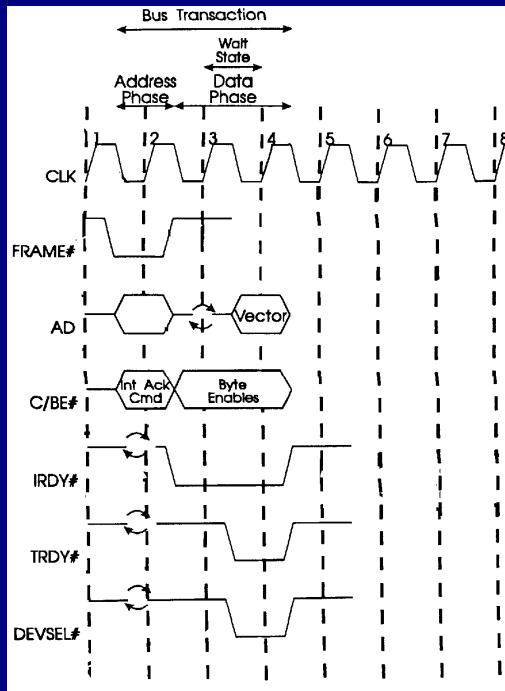

# Ciclo de Barramento Típico

Copyright © 2001 Walter Fetter Lages

29

## Comandos

- Reconhecimento de interrupção (0000)

- Ciclo especial (0001)

- Leitura de I/O (0010)

- Escrita de I/O (0011)

- Leitura de memória (0110)

- Escrita de memória (0111)

Copyright © 2001 Walter Fetter Lages

30

# Comandos

- Leitura de configuração (1010)

- Escrita de configuração (1011)

- Leitura múltipla de memória (1100)

- Ciclo dual–address (1101)

- Leitura de linha de memória (1110)

- Escrita de memória e invalidação (1111)

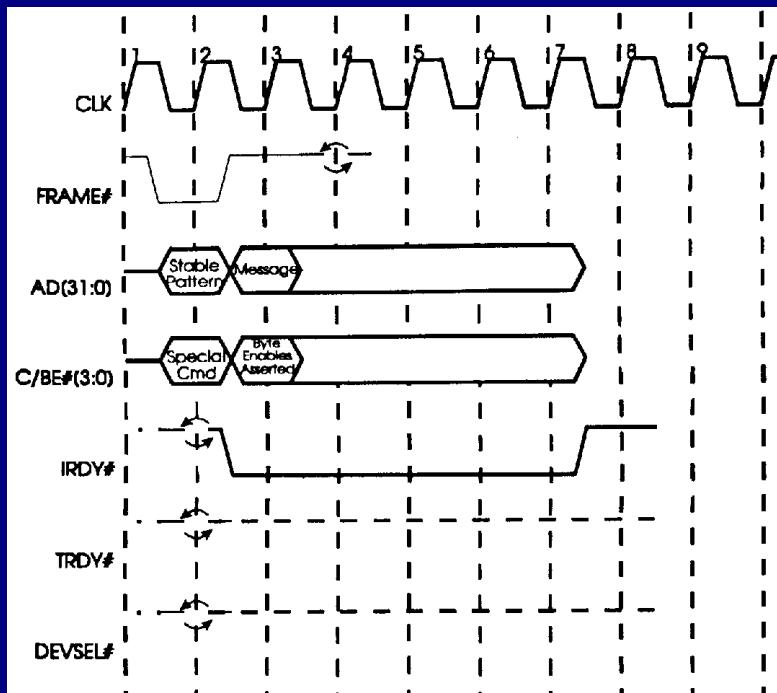

# Reconhecimento de Interrupção

- Bridge Host/PCI:

- Sinaliza ciclo de reconhecimento de interrupção

- Ativa #IRDY

- Target controlador de interrupções:

- Mantém #TRDY desativado por 1 ciclo

- Turn-around dos drivers da bridge

- Reclama a transação (ativa #DEVSEL)

- Insere o vetor de interrupções

- Ativa #TRDY

# Ciclo INTA

Copyright © 2001 Walter Fetter Lages

33

## Ciclo Especial

- Utilizado para difundir uma mensagem

- Nenhum target reclama a transação

- Initiator deve abortar a transação

- Códidos de mensagem em AD[15:0]

- 0000h = Shutdown

- 0001h = Halt

- 0002h = mensagem específica do ix86.

- AD[31:16] contém código específico da Intel

Copyright © 2001 Walter Fetter Lages

34

# Ciclo Especial

Copyright © 2001 Walter Fetter Lages

35

## Leitura de Memória

- Reg. de Cache Line Size implementado:

- Leitura: até 1/2 linha de cache

- Leitura de linha: de 1/2 a 3 linhas de cache

- Leitura múltipla: mais de 3 linhas de cache

- Reg. de Cache Line Size não implementado:

- Leitura: até 2 transferências de dados

- Leitura de linha: de 3 a 12 transferências

- Leitura múltipla: mais de 12 transferências

Copyright © 2001 Walter Fetter Lages

36

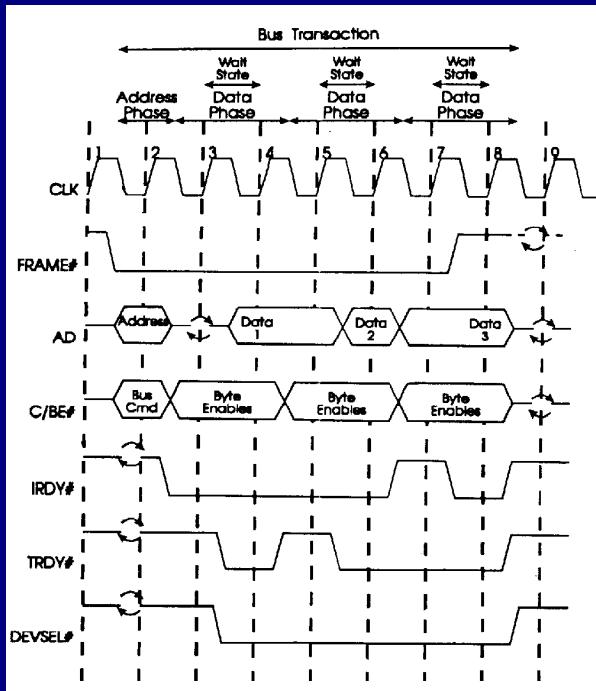

# Ciclo de Leitura

Copyright © 2001 Walter Fetter Lages

37

# Escrita em Memória

## ● Escrita

- Quando o target ativa o #TRDY ele assume a responsabilidade por manter a coerência dos dados

## ● Escrita e Invalidação

- Initiator está indicando que está escrevendo toda uma linha de cache

- Elimina a necessidade de back-off e line flush

Copyright © 2001 Walter Fetter Lages

38

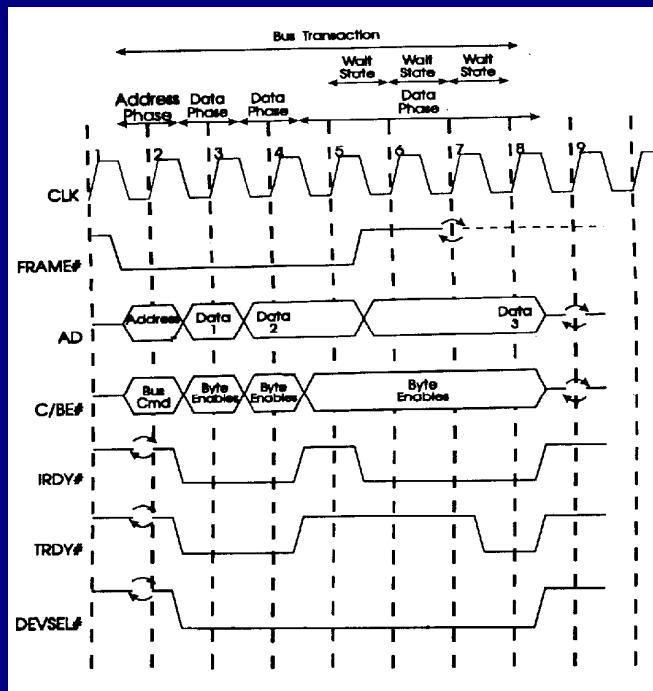

# Ciclo de Escrita

Copyright © 2001 Walter Fetter Lages

39

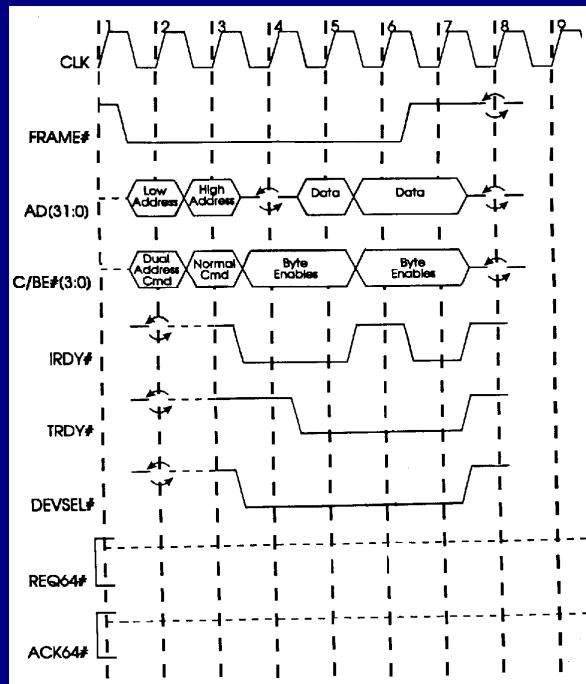

## Outros Ciclos

- Leitura e escrita de I/O

- Leitura e escrita de configuração

- Sinalizados por IDSEL

- Normalmente requer mapeamento nos espaços de endereçamento do processador

- Dual-address

- Utilizado para endereçamento de 64 bits

Copyright © 2001 Walter Fetter Lages

40

# Bridge Host/PCI

- Prefetch buffers

- Posting buffers

Copyright © 2001 Walter Fetter Lages

41

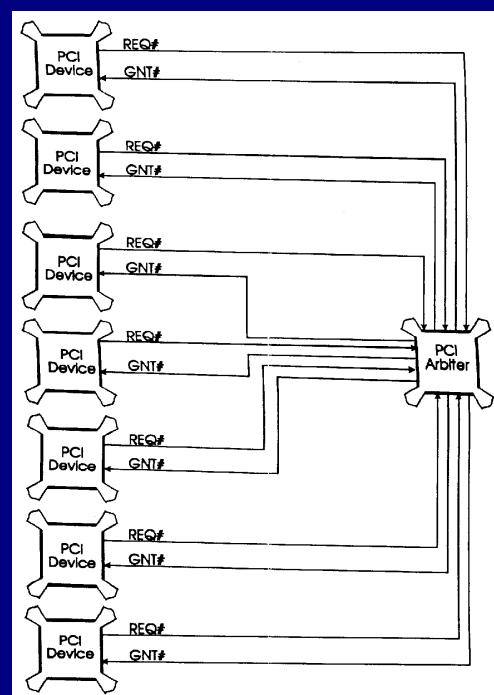

- REQ#

- GNT#

- Desativar REQ# ou GNT# não aborta a transação corrente, apenas sinalizam que o barramento será liberado ao final dela.

Copyright © 2001 Walter Fetter Lages

# Aborto de Transações

- Pelo initiator

- Transação completada normalmente

- Latency time-out e GNT# removido

- Nenhum target responde

- Pelo target

- Disconnect -> ocorre transferência de dados

- Retry

- Erro fatal

Copyright © 2001 Walter Fetter Lages

43

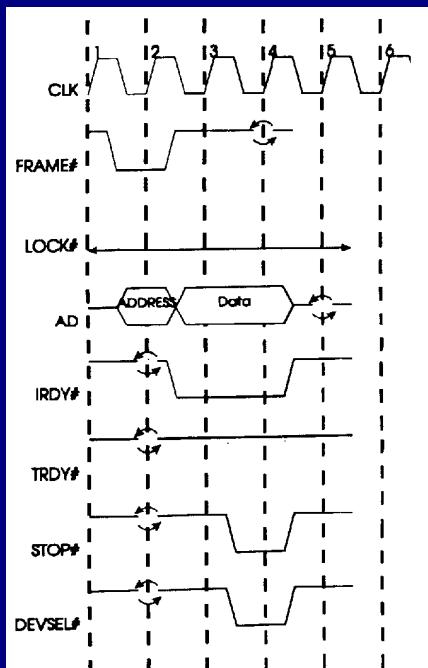

## Lock

Copyright © 2001 Walter Fetter Lages

44

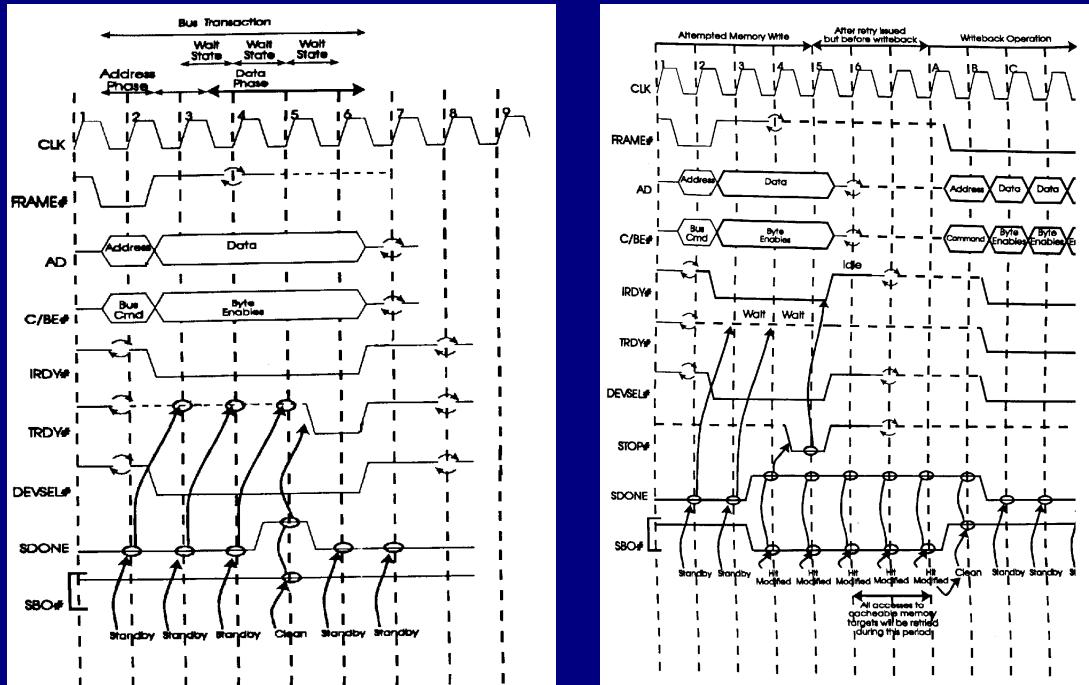

# Suporte a Cache

- Problema: O que acontece com o cache quando um operação de acesso à memória é iniciada no barramento PCI

- Cache Write-through – a linha de cache deve ser invalidada se for uma operação de escrita e ocorrer um snoop-hit

- Cache Write-back – se ocorrer um snoop-hit, a linha de cache deve ser limpa e se for uma operação de escrita a linha de cache deve ser invalidada

Copyright © 2001 Walter Fetter Lages

45

## Suporte a cache

- SDONE

- Indica que o snoop foi feito

- O target não deve aceitar o dado até que SDONE esteja ativo

- SBO#

- Indica que houve um hit em uma linha modificada

- Força o target a sinalizar um retry para o initiator

- A bridge mantém SBO# ativo até completar o write-back

Copyright © 2001 Walter Fetter Lages

46

# Snooping

Copyright © 2001 Walter Fetter Lages

47

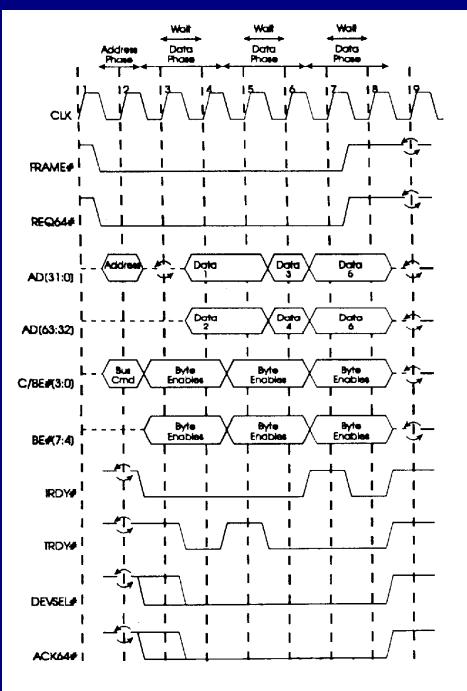

## Transferência de 64 bits

Copyright © 2001 Walter Fetter Lages

48

# Endereçamento de 64 bits

Copyright © 2001 Walter Fetter Lages

49

## Espaço de Configuração

| 31                                         | 16 15                   | 0               |                |

|--------------------------------------------|-------------------------|-----------------|----------------|

| <b>Device ID</b>                           | <b>Vendor ID</b>        | 00h             |                |

| <b>Status Register</b>                     | <b>Command Register</b> | 04h             |                |

| <b>Class Code</b>                          | <b>Revision ID</b>      | 08h             |                |

| BIST                                       | <b>Header Type</b>      | 0Ch             |                |

|                                            | Latency Timer           | Cache Line Size |                |

| Base Address 0                             |                         |                 |                |

| 10h                                        |                         |                 |                |

| Base Address 1                             |                         |                 |                |

| 14h                                        |                         |                 |                |

| Base Address 2                             |                         |                 |                |

| 18h                                        |                         |                 |                |

| Base Address 3                             |                         |                 |                |

| 1Ch                                        |                         |                 |                |

| Base Address 4                             |                         |                 |                |

| 20h                                        |                         |                 |                |

| Base Address 5                             |                         |                 |                |

| 24h                                        |                         |                 |                |

| Reserved (base address register expansion) |                         |                 |                |

| 28h                                        |                         |                 |                |

| Reserved (base address register expansion) |                         |                 |                |

| 2Ch                                        |                         |                 |                |

| Expansion ROM Base Address                 |                         |                 |                |

| 30h                                        |                         |                 |                |

| Reserved                                   |                         |                 |                |

| 34h                                        |                         |                 |                |

| Reserved                                   |                         |                 |                |

| 38h                                        |                         |                 |                |

| Max_Lat                                    | Min_Gnt                 | Interrupt Pin   | Interrupt Line |

| 3Ch                                        |                         |                 |                |

**Required configuration registers**

Copyright © 2001 Walter Fetter Lages

50

# Tratamento de Erros

- Erros de paridade

- PERR#

- Erro sinalizado no registrador de status

- Ativação ou não de PERR# é configurada no registrador de comando

- Erros de Sistema

- SERR#

- Somente pode ser ativado se configurado no registrador de comando

Copyright © 2001 Walter Fetter Lages

51

# Interrupções

- Ativas por nível

- Ativas em nível lógico baixo

- Compartilháveis

- Dispositivos que utilizem uma única interrupção devem utilizar INTA#

Copyright © 2001 Walter Fetter Lages

52

# Generalidades PCI

- Decodificação subtrativa

- A bridge PCI/ISA realiza decodificação subtrativa em todos os endereços de I/O abaixo de 64KB e todos os endereços de memória abaixo de 16MB

- Transações nos endereços ISA válidos sempre são efetivadas

- Palette snooping

- Quando se tem VGA on-board, a bridge monitora os acessos palette passa também para o barramento de expansão (slot)

Copyright © 2001 Walter Fetter Lages

53

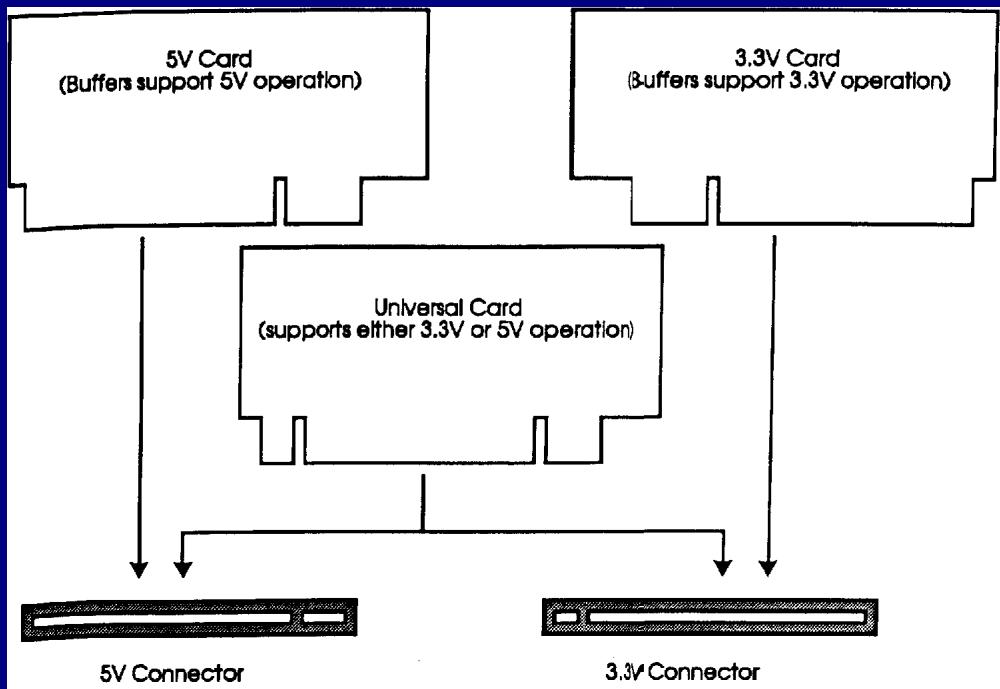

## Accelerated Graphics Port

- AGP é baseado na versão de 66MHz do PCI

- 32 bits apenas, versões de 3.3V e 1.5V

- Barramento com um único initiator (placa AGP) e um único target (CPU/bridge PCI)

- Extensões:

- Desacoplamento da fase de solicitação (endereçamento) da fase de dados

- Podem ser utilizadas as bordas de subida e de descida dos strobes para transferir dados

- Existem dois strobes

Copyright © 2001 Walter Fetter Lages

54

# Arquitetura do Sistema AGP

Copyright © 2001 Walter Fetter Lages

55

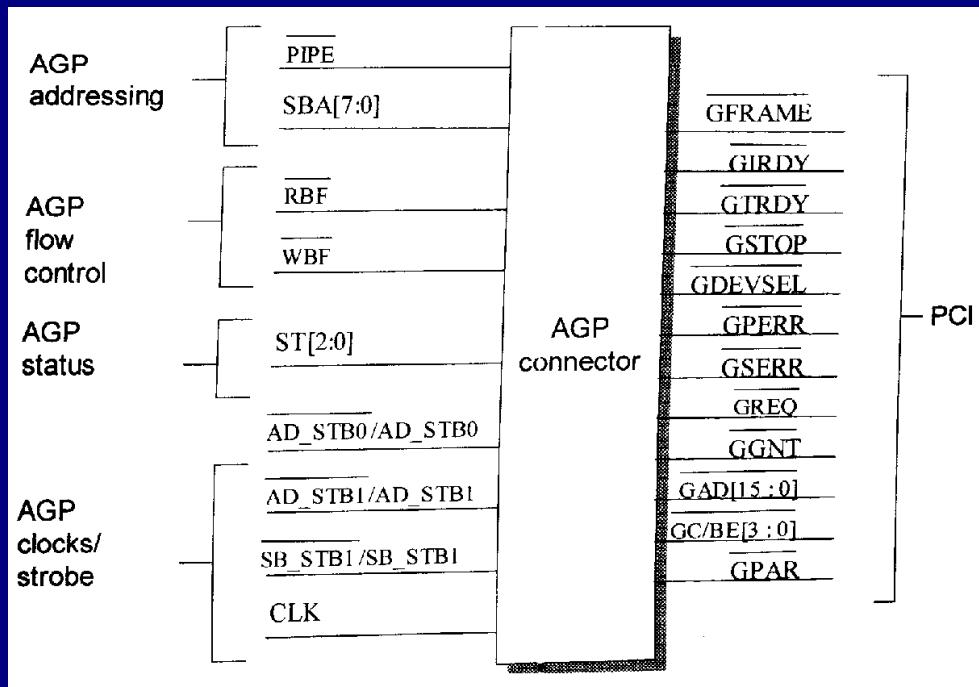

## Sinais AGP

Copyright © 2001 Walter Fetter Lages

56

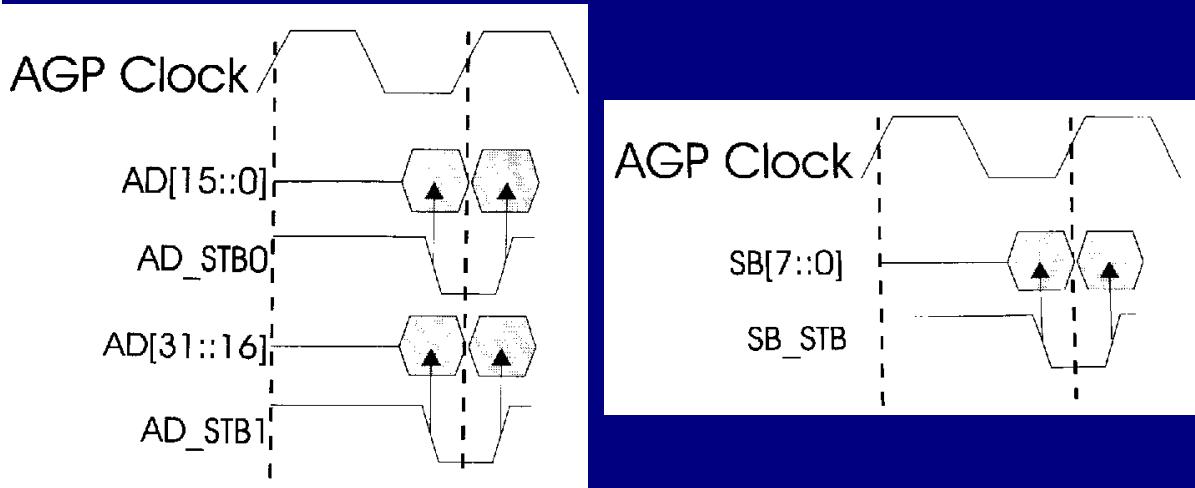

# Strobe no Modo 2x

- 2 transferências por ciclo de clock

$-66 * 4 * 2 = 528 \text{ MB/s}$

Copyright © 2001 Walter Fetter Lages

57

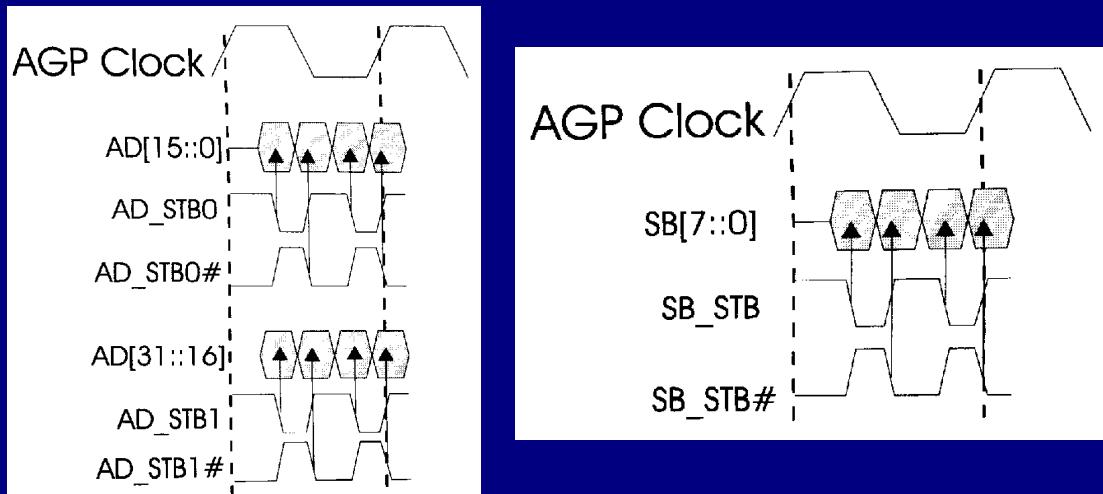

# Strobes no Modo 4x

- 4 transferências por ciclo de clock

$-66 * 4 * 4 = 1056 \text{ MB/s}$

Copyright © 2001 Walter Fetter Lages

58