## Interrupções e DMA

Copyright © 2001 Walter Fetter Lages

1

## Mecanismos de I/O

- Programmed I/O (PIO)

- Instruções privilegiadas

- Polling

- Interrupções

- Acesso direto à memória (DMA)

- Chanal de I/O

Copyright © 2001 Walter Fetter Lages

2

# Interrupções

- Mascaráveis

- Podem ser desabilitadas

- Não mascaráveis

- Não podem ser desabilitadas

- Ativas por borda

- Solicitação ativa quando ocorre transição (subida ou descida) do sinal

- Ativas por nível

- Solicitação ativa quando o sinal está em um determinado nível (alto ou baixo)

Copyright © 2001 Walter Fetter Lages

3

# Interrupções

- Latência

- Prioridade

- Traps

- Interrupções de *software*

- Interface com o sistema operacional

- Exceções

- Geradas internamente pelo processador

Copyright © 2001 Walter Fetter Lages

4

# Interrupções no 80x86

- Interrupção mascarável

- Solicitada através do pino INTR

- Se estiver habilitada, após terminar a execução da instrução atual o processador reconhece a interrupção

- A CPU ativa o pino INTA# por um ciclo de barramento para reconhecer a interrupção

- A CPU ativa o pino INTA# em outro ciclo de barramento para obter o vetor de interrupção

- O vetor de interrupção é utilizado como índice na IDT para obter o endereço da rotina de tratamento

Copyright © 2001 Walter Fetter Lages

5

# Interrupções no 80x86

- Interrupção não-mascarável

- Solicitada através do pino NMI

- Após terminar a execução da instrução atual o processador desvia para a rotina de tratamento apontada na entrada 2 da IDT

- Interrupção de software

- Gerada através da instrução INT n

- Não podem ser desabilitadas

Copyright © 2001 Walter Fetter Lages

6

# NMI no PC

- Pode ser desabilitada através de um flip-flop no bit 0 da porta 70h

- Erro de paridade na memória

- Erro no barramento ISA (IOCHK#)

- Erro no co-processador

- Erro de sistema no barramento PCI (SERR#)

- Opcional

Copyright © 2001 Walter Fetter Lages

7

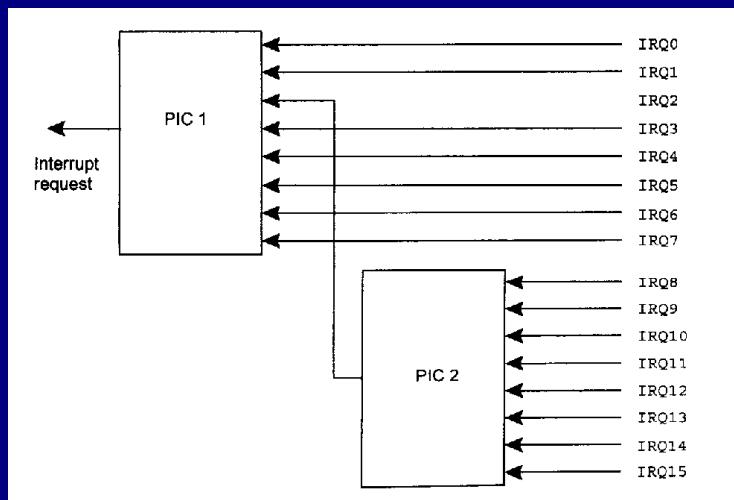

# Interrupções no PC

- 2 controladores 8259A em cascata

- Implementados no Chipset

Copyright © 2001 Walter Fetter Lages

8

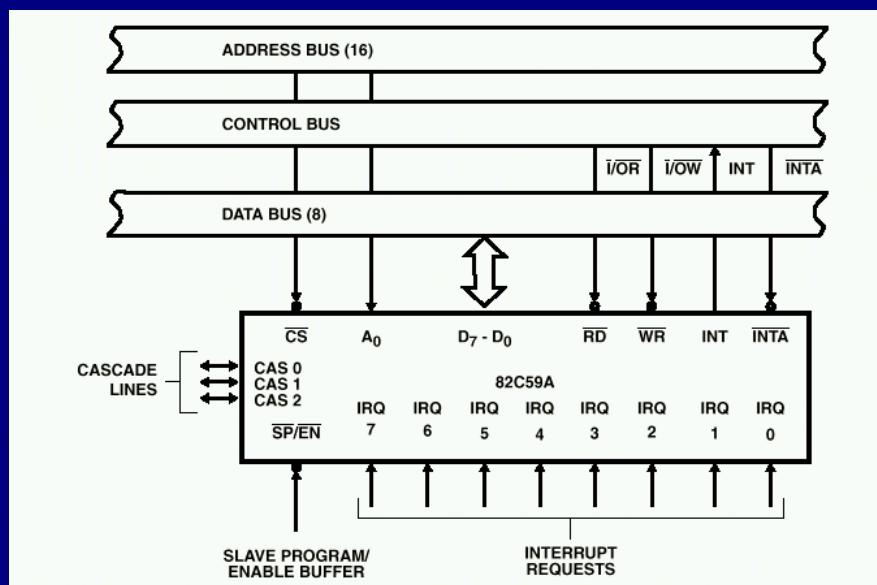

# 8259A

- IRQs podem ser habilitadas/desabilitadas individualmente

- Vetores de interrupção em seqüência

- O sinal IRQ deve ficar ativo até após o início do primeiro pulso INTA#

- Caso contrário o 8259 assume uma interrupção espúria, que é mapeada para IRQ7

- O software deve estar preparado para tratar esta situação

Copyright © 2001 Walter Fetter Lages

9

## Interface do 8259A

Copyright © 2001 Walter Fetter Lages

10

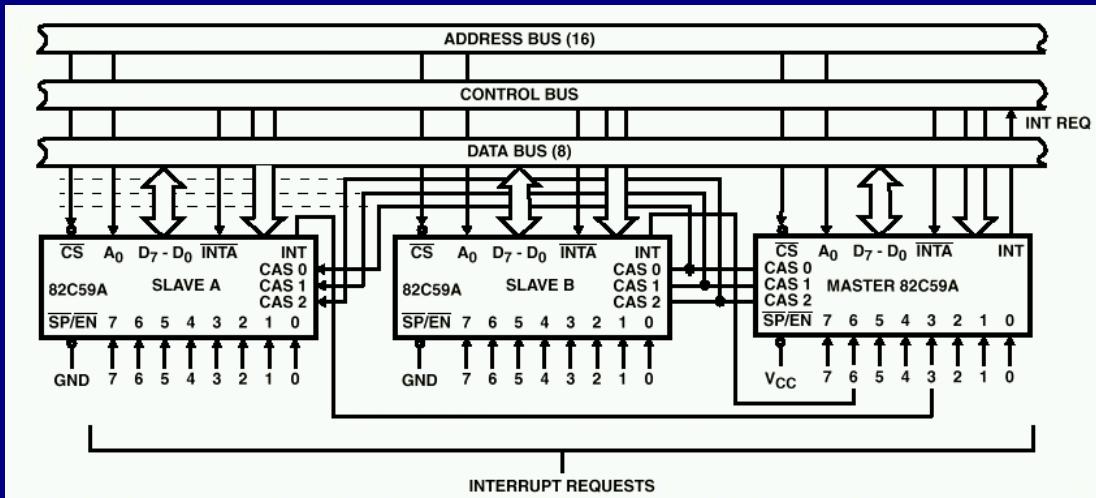

# Cascadeamento de 8259As

Copyright © 2001 Walter Fetter Lages

11

## Inicialização do 8259A no PC

- Interrupções ativas por borda

- Prioridade fixa

- 0, 1, (2), 3, 4, 5, 6, 7

- ^ 8, 9, 10, 11, 12, 13, 14, 15

- Base dos vetores de interrupção

- PIC1 = 08h

- IRQ0 ~ INT 8h

- PIC2 = 70h

- IRQ8 ~ INT 70h

- Coincidência de vetores do PIC1 com TRAPs de modo protegido

- Sistema Operacional reprograma base dos vetores

Copyright © 2001 Walter Fetter Lages

12

# Interrupções no XT

- O XT tem apenas um 8259A

- No slot ISA, a IRQ9 ocupa o lugar da IRQ2 que existia no slot do XT

- Redirecionamento por software da rotina de tratamento da IRQ9 para IRQ2

- A rotina de tratamento de IRQ9 executa um INT 10h

Copyright © 2001 Walter Fetter Lages

13

# Interrupções ISA

- IRQ0 timer

- IRQ1 teclado

- IRQ2 cascata

- IRQ3 COM2/COM4

- IRQ4 COM1/COM3

- IRQ5 LPT2/HD-XT

- IRQ6 floppy

- IRQ7 LPT1

- IRQ8 RTC

- IRQ9 livre/VGA

- IRQ10 livre

- IRQ11 livre

- IRQ12 livre/PS2

- IRQ13 FPU

- IRQ14 IDE

- IRQ15 livre/IDE2

Copyright © 2001 Walter Fetter Lages

14

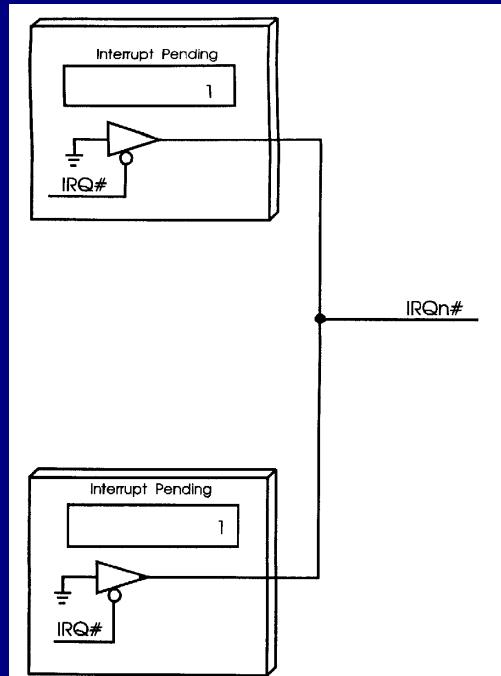

# Compartilhamento de IRQs

- Pela especificação do barramento ISA, as IRQs devem ser geradas por um circuito em coletor aberto

- IRQs deveriam poder ser compartilhadas

- Poucos fabricantes implementam corretamente o circuito de geração de IRQ

- Compartilhamento apenas seria possível se fossem ativas por nível (EISA)

- Poucos drivers estão preparados para possibilitar o compartilhamento de IRQs

Copyright © 2001 Walter Fetter Lages

15

# Compartilhamento de IRQs

Copyright © 2001 Walter Fetter Lages

16

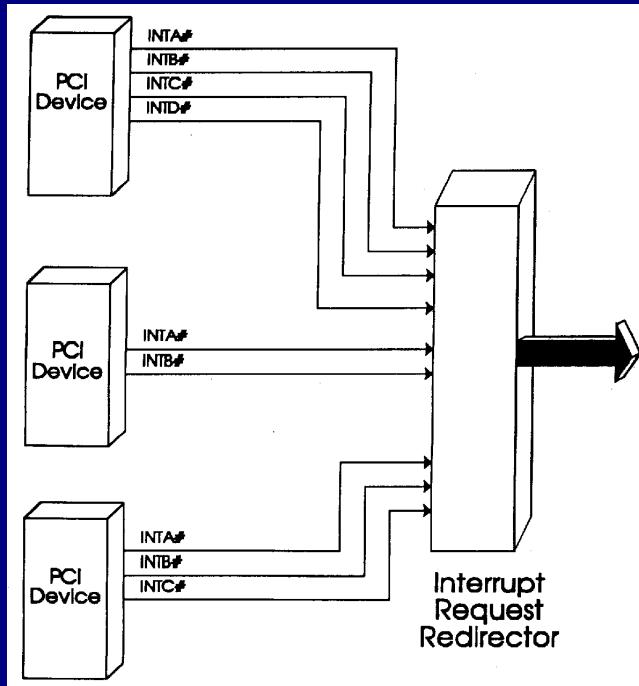

# Interrupções PCI

- 4 linhas de requisição de interrupção

- INTA#, INTB#, INTC#, INTD#

- Ativas por nível, ativas em baixo, compartilháveis

- Dispositivos PCI com uma única função devem utilizar INTA#

- Cada função deve utilizar apenas uma linha de requisição de interrupção

Copyright © 2001 Walter Fetter Lages

17

# Interrupções PCI

Copyright © 2001 Walter Fetter Lages

18

# Roteamento de Interrupções

- As interrupções PCI devem ser roteadas para o controlador de interrupções

- Cada função PCI que utiliza interrupção deve implementar dois registradores de configuração

- Interrupt Pin Register (R/O)

- Interrupção PCI

- Interrupt Line Register (R/W)

- Linha de IRQ a ser utilizada

Copyright © 2001 Walter Fetter Lages

19

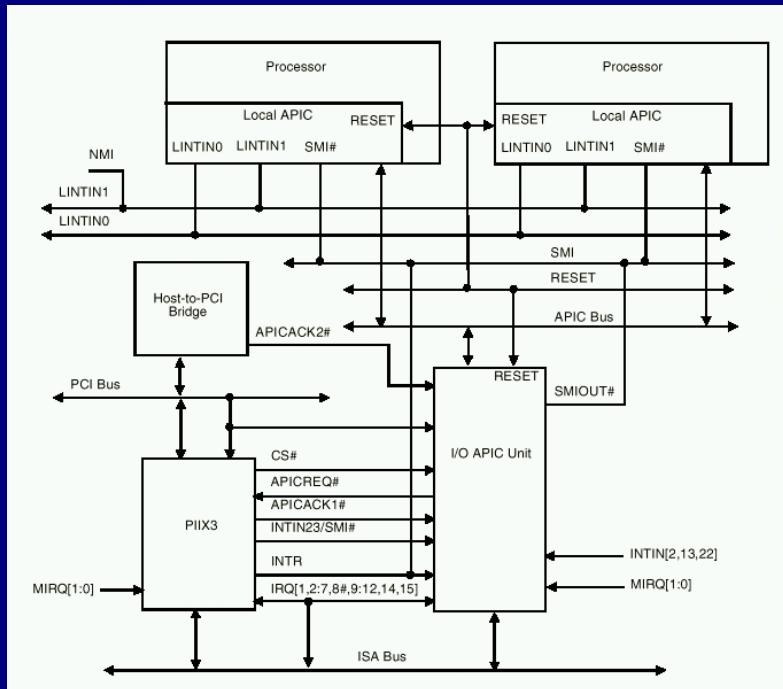

## APIC

- APIC=Advanced Programmable Interrupt Controller

- Desenvolvido para ser utilizado em sistemas com mais de um processador

- Pode ser utilizado em sistemas uniprocessador

- Menor latência do que o controlador com 8259A

- Pode ser utilizado conjuntamente com o 8259A

- Cada controlador controla algumas interrupções

- Suporta a distribuição das interrupções entre os processadores

Copyright © 2001 Walter Fetter Lages

20

# Sistema APIC

- Composto por duas partes que se comunicam através do barramento APIC

- Local APIC

- Localizado em cada processador

- Determina se o processador deve processar a interrupção difundida no barramento APIC

- Gera interrupções entre os processadores

- Possui um temporizador

- I/O APIC

- Suporta linhas de interrupção para os periféricos

- Possui tabela de redirecionamento de interrupções

Copyright © 2001 Walter Fetter Lages

21

## Tabela de Redirecionamento

- Armazena as características de cada linha de interrupção

- Ativa por borda ou por nível

- Vetor de interrupção

- Prioridade

- Processador de destino

- Seleção de processador estática ou dinâmica

- Estática = interrupção associada ao processador

- Dinâmica = processador selecionado dinamicamente

Copyright © 2001 Walter Fetter Lages

22

# Barramento APIC

Copyright © 2001 Walter Fetter Lages

23

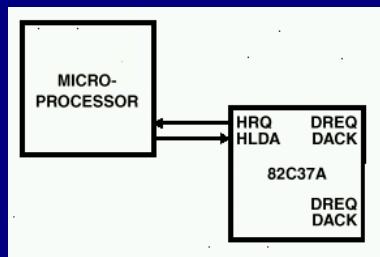

## Acesso Direto à Memória

- Frequentemente utilizado com interrupções para sinalizar o fim da transferência de um bloco de dados

- O controlador de DMA assume o controle do barramento e faz a transferência

Copyright © 2001 Walter Fetter Lages

24

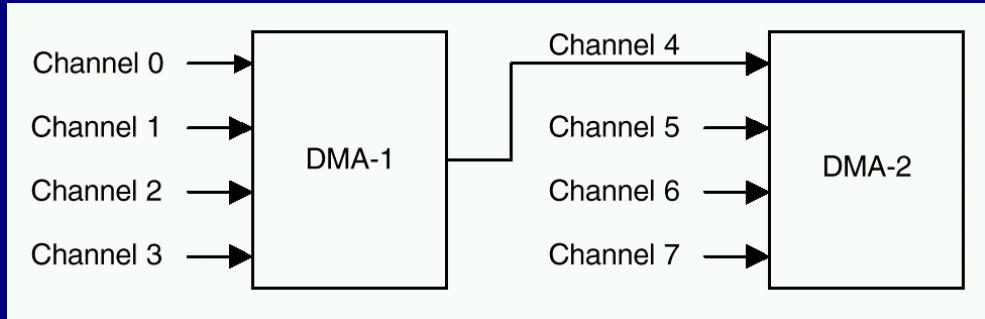

# DMA no PC

- O PC utiliza dois 8237A em cascata e um registrador de página para armazenar os bits mais significativos de endereço

- Páginas de 64 KB para o escravo e 128KB para o mestre

- Bus-master ISA é feito através do DMA

Copyright © 2001 Walter Fetter Lages

25

## Modos de DMA ISA

- Transferência única

- Uma transferencia a cada requisição

- Transferência em bloco

- Um bloco transferido por requisição

- Transferência por demanda

- Tranferências enquanto a requisição estiver ativa

- Transferência memória–memória

Copyright © 2001 Walter Fetter Lages

26

# Canais de DMA ISA

- Escravo – 8 bits

- 0 refresh no XT/Sound Blaster/ECP

- 1 Sound Blaster

- 2 floppy

- 3 IDE/ECP

- Mestre – 16 bits

- 4 cascata

- 5 Sound Blaster

- 6

- 7

Copyright © 2001 Walter Fetter Lages

27

## Otimizações do DMA

- Dependentes do Chipset

- Transferências de 16/32 bits em todos os canais

- Capacidade de endereçar com 32 bits

- Preempção

- Scatter-write e gather-read (buffer chaining)

Copyright © 2001 Walter Fetter Lages

28

# DMA PCI

- DMA PC/PCI

- Linhas de REQUEST e GRANT dedicadas

- Associa um canal de DMA à um mestre PCI

- DMA distribuído

- Emulação de um 8237 através de canais de DMA implementados nos dispositivos PCI

- O chipset monitora os acessos ao 8237 virtual e distribui os dados no barramento PCI

- Cada canal DMA pode ser configurado

- DMA ISA

- DMA PC/PCI

- DMA distribuído

Copyright © 2001 Walter Fetter Lages